Эвалюцыя транзістараў: ад планарнага да CFET, 3D-інтэграцыя пераасэнсоўвае прагрэс паўправаднікоў

Больш за паўстагоддзя паўправадніковая прамысловасць развівалася, прытрымліваючыся аднаго простага правіла: рабіце транзістары меншымі.Памяншэнне памераў функцый забяспечвае больш высокую прадукцыйнасць, меншую магутнасць і меншы кошт транзістара.Але сёння гэты шлях дасягнуў сваёй фізічнай і эканамічнай мяжы.Эра чыстага маштабавання скончылася, і наступіла новая эра структурныя інавацыі і 3D інтэграцыя пачалося.

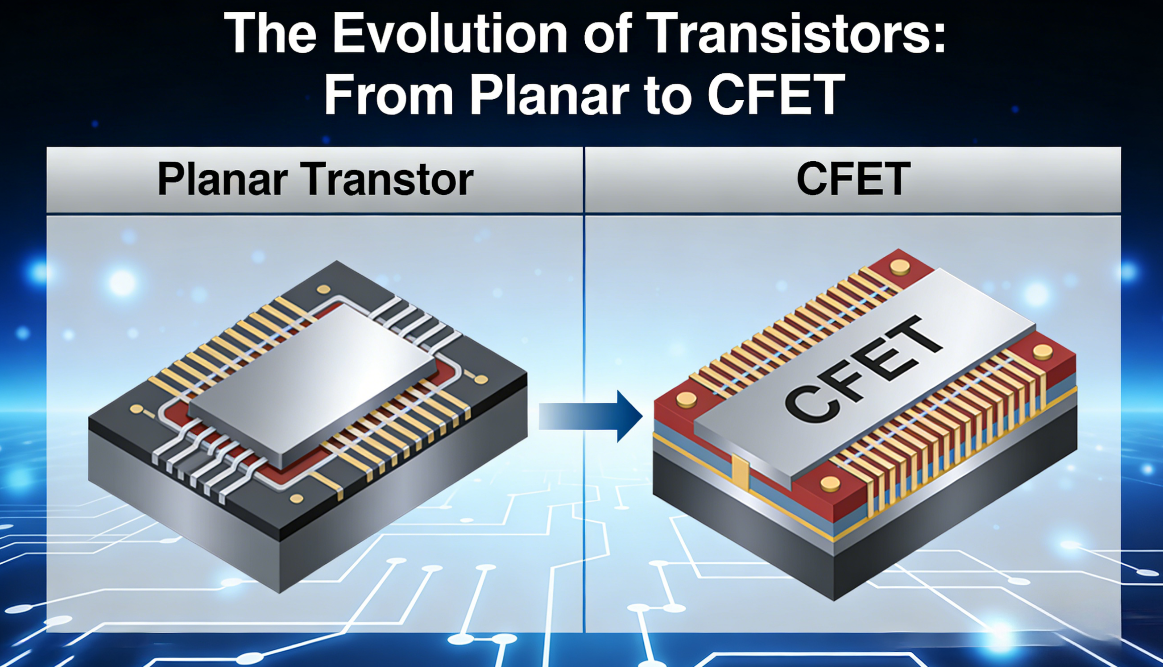

Сам транзістар перажывае поўную архітэктурную рэвалюцыю.Ад планарнага MOSFET да FinFET, ад наналіста GAA да кладкі CFET, кожны крок уяўляе сабой пераход ад сціскання да перабудова транзістара ў трох вымярэннях.Гэта не проста паступовае паляпшэнне — гэта поўнае перавызначэнне таго, як чыпы забяспечваюць прадукцыйнасць.

Чатыры пакаленні транзістарнай архітэктуры

1. Планарны транзістар (традыцыйны 2D)

Класічная плоская канструкцыя, дзе засаўка кантралюе канал зверху.Ён дамінаваў з першых дзён да 40 нм і 28 нм.Па меры далейшага змяншэння памераў ток уцечкі і электрастатычны кантроль сталі невырашальнымі праблемамі.

2. FinFET (3D Gate Control)

Канал становіцца вертыкальным «плаўніком», з варотамі, абгорнутымі вакол трох бакоў.Гэта істотна паляпшае электрастатычны кантроль, памяншае ўцечку і дазваляе паменшыць маштаб да 7 нм, 5 нм і нават 3 нм.FinFET стаў асновай сучаснай эры высокапрадукцыйных чыпаў.

3. GAA Nanosheet (Gate-All-Around)

Пры 2 н і ніжэй FinFET дасягае свайго ліміту.GAA замяняе плаўнік на складзеныя гарызантальныя нанаправады або лісты, цалкам акружаныя варотамі.Гэта забяспечвае лепшы кантроль, меншую магутнасць і больш высокі ток прывада.Цяпер GAA з'яўляецца асноўнай структурай для чыпаў класа 2 нм у TSMC, Samsung і Intel.

4. CFET (дадатковы FET)

Наступная мяжа: вертыкальнае размяшчэнне NMOS і PMOS.CFET змяшчае два транзістары ў адзін, рэзка памяншаючы плошчу і паляпшаючы шчыльнасць.Гэта канчатковы канец эвалюцыйнага маштабавання транзістараў перад тым, як сапраўдная 3D-сістэмная інтэграцыя возьме верх.

Чаму толькі маштабаванне больш не працуе

- Кошт працэсу расце ў геаметрычнай прагрэсіі з кожным новым вузлом

- Квантавая ўцечка і фізічныя абмежаванні ўзмацняюць межы

- Затрымка злучэння і энергаспажыванне перавышаюць хуткасць транзістара

- Буйная маналітная дранка пакутуе ад нізкай ураджайнасці і высокай кошту

Прамысловасць зразумела: прадукцыйнасць больш не залежыць ад меншых транзістараў.Гэта адбываецца ад лепшыя сувязі, больш разумная архітэктура і вертыкальная інтэграцыя.

Новая эра: тры ўзроўні 3D-інавацый

Прагрэс паўправаднікоў цяпер вызначаецца трыма вымярэннямі 3D-дызайну:

- 3D транзістар: FinFET, GAA, CFET - стварэнне транзістара вертыкальна

- 3D-складанне прылад: лагічная памяць, гібрыднае злучэнне, стэкаванне SRAM

- Сістэмная інтэграцыя 3D: Chiplet, упакоўка 2.5D/3D, інтэграцыя на аснове інтэрпазера

Разам яны ўтвараюць 3D×3D×3D эра: транзістар, прылада і сістэма становяцца трохмернымі.

DTCO: новая асноўная кампетэнцыя

Калі маштабаванне заканчваецца, Кааптымізацыя тэхналогій праектавання (DTCO) становіцца крытычным.Гэта азначае сумеснае праектаванне архітэктуры, структуры транзістараў, пракладкі металу і ўпакоўкі з самага пачатку.Наймацнейшыя кампаніі больш не проста лідэры працэсаў — яны інтэгратары сістэмнага ўзроўню.

Эфектыўнасць праводкі, падача энергіі, цеплавая канструкцыя і шчыльнасць паласы прапускання цяпер вызначаюць рэальную прадукцыйнасць прадукту.

ШІ з'яўляецца найвышэйшай рухаючай сілай

ШІ і высокапрадукцыйныя вылічэнні патрабуюць беспрэцэдэнтнай прапускной здольнасці, энергаэфектыўнасці і шчыльнасці.Гэтыя патрабаванні не могуць быць задаволены традыцыйным маштабаваннем.Яны патрабуюць:

- Звышвысокая прапускная здольнасць памяці-вылічальнага злучэння

- Надзвычайная энергаэфектыўнасць на аперацыю

- Масавы паралелізм і шчыльная інтэграцыя

ШІ прымусіў усю галіну адмовіцца ад чыстага маштабавання і прыняць поўную 3D-неаднародную інтэграцыю.

Выснова: будучыня не меншая, яна вышэйшая

Эпоха скарачэння транзістараў сыходзіць у нябыт.Будучыня паўправаднікоў заключаецца не ў памяншэнні прылад, а ў стварэнні сістэм вышэй, шчыльней і больш разумна звязаны.

Ад Planar да FinFET і GAA да CFET транзістар завяршыў сваю эвалюцыю.Наступны бой адбудзецца ў 3D-інтэграцыя, пашыраная ўпакоўка і дызайн на сістэмным узроўні.Тут будзе вызначана наступнае дзесяцігоддзе лідэрства ў галіне паўправаднікоў.